# LIQUID CRYSTAL DISPLAY MODULE

# **Product Specification**

| CUSTOMER                | Standard         |

|-------------------------|------------------|

| CUSTOMER<br>PART NUMBER |                  |

| PRODUCT<br>NUMBER       | DBC-32024041-1A0 |

| Product Mgr     | Design Eng      |  |  |

|-----------------|-----------------|--|--|

| Bruno Recaldini | Luo Luo         |  |  |

| Date: 15-Feb-12 | Date: 15-Feb-12 |  |  |

| Product No. DBC-32024041-1A0 REV. 1.1 Page 1/   |    |

|-------------------------------------------------|----|

|                                                 | 10 |

| Product No. DBC-32024041-TAU REV. 1.1   Page 1/ | 40 |

# TABLE OF CONTENTS

| 1 | Μ                                                 | AIN FEATURES                                                                       | .4       |

|---|---------------------------------------------------|------------------------------------------------------------------------------------|----------|

| 2 | Μ                                                 | ECHANICAL SPECIFICATION                                                            | .5       |

|   | 2.1<br>2.2<br>2.3                                 | MECHANICAL CHARACTERISTICS<br>MECHANICAL DRAWING<br>SERIAL LABEL / PRINT           | .6<br>.7 |

| 3 | EI                                                | LECTRICAL SPECIFICATION                                                            |          |

|   | <ol> <li>3.1</li> <li>3.2</li> <li>3.3</li> </ol> | ABSOLUTE MAXIMUM RATINGS<br>ELECTRICAL CHARACTERISTICS<br>INTERFACE PIN ASSIGNMENT | .8       |

|   | 3.4                                               | TIMING CHARACTERISTICS                                                             |          |

|   | 3.5<br>3.6                                        | DESCRIPTION OF OPERATION                                                           | 88       |

| 4 | O                                                 | PTICAL SPECIFICATION4                                                              | 0        |

|   | 4.1                                               | OPTICAL CHARACTERISTICS4                                                           | 0        |

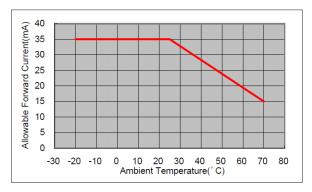

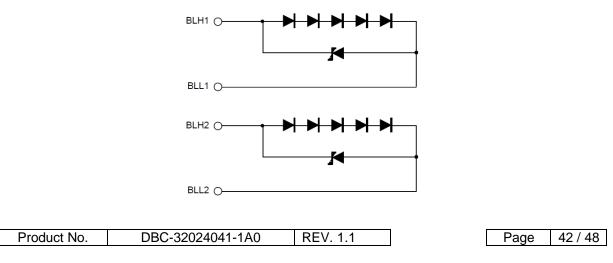

| 5 | BA                                                | ACKLIGHT SPECIFICATION4                                                            | 2        |

|   | 5.1<br>5.2                                        | LED DRIVING CONDITIONS                                                             |          |

| 6 | Q                                                 | UALITY ASSURANCE SPECIFICATION4                                                    | 3        |

|   | 6.1<br>6.2<br>6.3                                 | DEFECTIVE DISPLAY AND SCREEN QUALITY                                               | 4        |

| 7 | RI                                                | ELIABILITY SPECIFICATION4                                                          | 6        |

|   | 7.1                                               | RELIABILITY TESTS4                                                                 | 6        |

| 8 | H                                                 | ANDLING PRECAUTIONS4                                                               | 8        |

Product No. DBC-32024041-1A0 REV. 1.1

Page 2 / 48

#### **REVISION RECORD**

| Rev. | Date       | Page | Chapt. | Comment                    | ECN no. |

|------|------------|------|--------|----------------------------|---------|

| 1    | 19.02.2010 |      |        | First Issue                |         |

| 1.1  | 15-Feb-12  | 7    | 2.3    | Added Serial Label / Print |         |

|      |            |      |        |                            |         |

|      |            |      |        |                            |         |

|      |            |      |        |                            |         |

Product No. DBC-32024041-1A0 REV. 1.1

Page 3 / 48

# **1 MAIN FEATURES**

| ITEM                  | CONTENTS                                  |

|-----------------------|-------------------------------------------|

| Screen Size           | 4.1" Diagonal                             |

| Display Format        | 320 x RGB x 240 Dots                      |

| N° of Colour          | 16.7 million                              |

| Overall Dimensions    | 90.31 mm (H) x 74.62 mm (V) x 3.13 mm (D) |

| Active Area           | 82.56 mm (H) x 61.92 mm (V)               |

| LCD Type              | TFT                                       |

| Mode                  | Sunlight Readable                         |

| Interface             | 6-bit / 8-bit RGB, parallel input         |

| Backlight Type        | LED                                       |

| Operating Temperature | -20°C ~ +70°C                             |

| Storage Temperature   | -30°C ~ +80°C                             |

| RoHS compliant        | Yes                                       |

Product No. DBC-32024041-1A0 REV. 1.1

Page 4 / 48

DENSITRON TECHNOLOGIES plc. – PROPRIETARY DATA – ALL RIGHTS RESERVED

# **2 MECHANICAL SPECIFICATION**

# 2.1 MECHANICAL CHARACTERISTICS

| ITEM               | CHARACTERISTIC                            | UNIT |

|--------------------|-------------------------------------------|------|

| Display Format     | 320 x RGB x 240 Dots                      | Dots |

| Overall Dimensions | 90.31 mm (H) x 74.62 mm (V) x 3.13 mm (D) | mm   |

| Bezel Opening Area | 85.26 (H) x 64.62 (V)                     | mm   |

| Active Area        | 82.56 mm (H) x 61.92 mm (V)               | mm   |

| Dot Pitch          | 86.0 (H) x RGB x 258.0 (V)                | μm   |

| Weight             | 42.4                                      | g    |

| Product No. | DBC-32024041-1A0 | REV. 1.1 |

|-------------|------------------|----------|

|             |                  |          |

Page 5 / 48

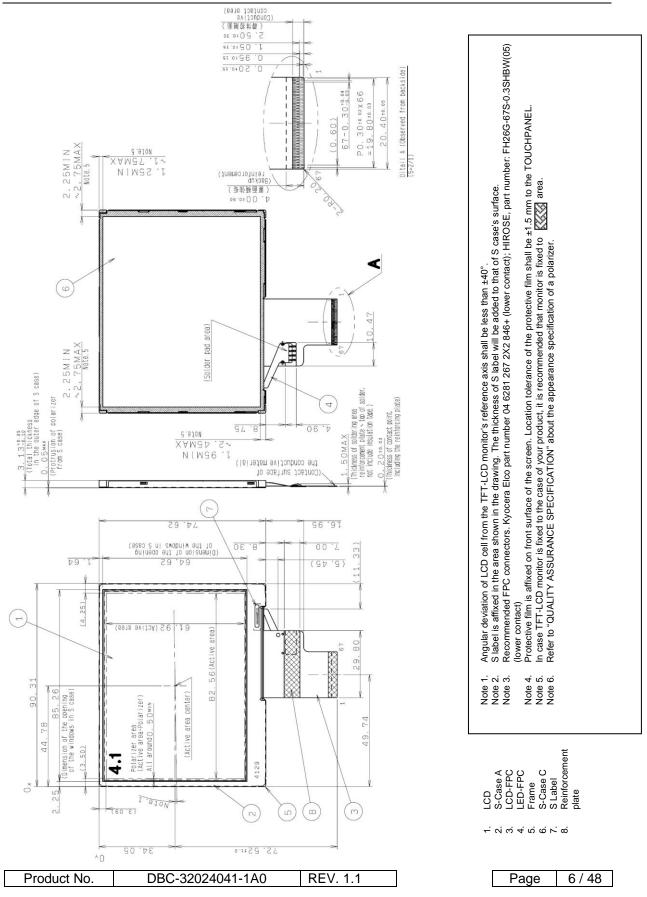

# 2.2 MECHANICAL DRAWING

7 / 48

# 2.3 SERIAL LABEL / PRINT

The label / print indicates the least significant digit of manufacture year (1digit), manufacture month with below alphabet (1letter), model code (4 or 5 characters), serial number (6 digits).

\* Label / Print Contents

\* \* \*\*\*\*(\*) \*\*\*\*\*\* a b c d

where:

- a The least significant digit of manufacturing year

- b Manufacturing Month: Jan-A, Feb-B, Mar-C, Apr-D, May-E, Jun-F, Jul-G, Aug-H, Sep-I, Oct-J, Nov-K, Dec-L

- c Model code 41BDC →Made in Japan 41BEC →Made in Malaysia 41BFC →Made in China

- d Serial number, like "000125"

Examples:

Made in Japan 2D41BDC000125 means "manufactured in April 2012, model 41BDC, serial number 000125"

Made in Malaysia 2D41BEC000125 means "manufactured in April 2012, model 41BEC, serial number 000125"

Made in China 2D41BFC000125 means "manufactured in April 2012, model 41BFC, serial number 000125"

Product No. DBC-32024041-1A0 REV. 1.1 Page

# **3 ELECTRICAL SPECIFICATION**

# 3.1 ABSOLUTE MAXIMUM RATINGS

| Item                      | Symbol | Condition | Min  | Мах     | Unit | Applicable terminal                                               |

|---------------------------|--------|-----------|------|---------|------|-------------------------------------------------------------------|

| Supply Voltage            | VDD    |           | -0.3 | 6.0     | V    | VDD                                                               |

| Input Voltage 1 for Logic | VI1    | Ta= 25°C  | -0.3 | VDD+0.3 | V    | POCB,CLK,VSYNC,<br>HSYNC,D[27:20],<br>D[17:10], D[07:00],<br>MODE |

| Input Voltage 2 for Logic | VI2    |           | -0.3 | 6.0     | V    | CS/STBY,DI/DE,<br>SCK/REV                                         |

# 3.2 ELECTRICAL CHARACTERISTICS

| Item                            | Symbol | Condition                              | Min  | Тур  | Max  | Unit | Applicable<br>terminal                                                    |

|---------------------------------|--------|----------------------------------------|------|------|------|------|---------------------------------------------------------------------------|

| Supply Voltage                  | VDD    | VDD                                    | 2.7  | 3.0  | 3.6  | V    | VDD                                                                       |

| Input Voltage 1 for Logic       | VI1    | VDD= 2.7~3.6V                          | 0    |      | VDD  | V    | POCB,CLK,<br>VSYNC,<br>HSYNC,<br>D[27:20],<br>D[17:10],<br>D[07:00], MODE |

| Input Voltage21 for Logic       | VI2    |                                        | 0    |      | VDD  | V    | CS/STBY,DI/DE<br>, SCK/REV                                                |

| Common electrode centre voltage | VCOMDC | MODE="VSS"<br>VDCOMDC[5:0]<br>=16h-C3h | 1.40 | 1.90 | 2.24 | V    | COMDC                                                                     |

| [Note 1]                        |        | MODE="VDD"                             | 1.40 | 1.90 | 2.24 | V    |                                                                           |

Note1:Common-electrode centre voltage indicates that optimum VCOMDC value lies within the bound of these voltages, but it does not mean the whole range of voltages are the optimum VCOMDC value

| Product No. | DBC-32024041-1A0 | REV. 1.1 |   | Page | 8 / 48 |

|-------------|------------------|----------|---|------|--------|

|             |                  |          | - |      |        |

#### (Unless otherwise noted, Ta=25°C, VDD=3.0V, VSS=0V)

| Item                      | Symbol | Condition                                                                                        | Min      | Тур      | Max      | Unit    | Applicable<br>terminal                                 |

|---------------------------|--------|--------------------------------------------------------------------------------------------------|----------|----------|----------|---------|--------------------------------------------------------|

|                           | VP     |                                                                                                  | 0.47xVDD | 0.60xVDD | 0.73xVDD | V       | CS/STBY,DI/DE,<br>SCK/REV,                             |

| Schmitt Threshold voltage | VN     |                                                                                                  | 0.30xVDD | 0.43xVDD | 0.56xVDD | V       | VSYNC, HSYNC,<br>D[27:20], D[17:10],<br>D[07:00], CLK, |

|                           | VH     |                                                                                                  | 0.08xVDD | 0.17xVDD | 0.27xVDD | V       | POCB                                                   |

| Input signal voltage      | VIH    |                                                                                                  | 0.7xVDD  | -        | VDD      | V       | MODE                                                   |

| input signal voltage      | VIK    | VDD=                                                                                             | 0        | -        | 0.3xVDD  | V       | MODE                                                   |

| Pull Up Resister Value    | Rpu    | 2.7~3.6V                                                                                         | 45       | 91       | 182      | kΩ      | РОСВ                                                   |

| Pull Down Resister Value  | Rpd    | -                                                                                                | 45       | 91       | 182      | kΩ      | MODE                                                   |

| Output voltage 1          | VDD2   |                                                                                                  | 4.8      | 5.6      | 6.1      | V       | VDD2                                                   |

| Output voltage 2          | VGH    |                                                                                                  | 12.5     | 13.3     | 13.5     | V       | VGH                                                    |

| Output voltage 3          | VGL    |                                                                                                  | -13.5    | -13.3    | -12.5    | V       | VGL                                                    |

| Output voltage 4          | VOH    | lo = -1.0mA                                                                                      | VDD-0.5  | -        | VDD      | V       | BLON                                                   |

| Output voltage 4          | VOL    | lo = 1.0mA                                                                                       | 0        | -        | 0.5      | V       | BLOW                                                   |

| Operating Current         | IDD    | fCLK=<br>6.75MHz<br>Colour bar<br>display<br>BRIGHT[5:0]<br>CONTRAST<br>[3:0] = Initial<br>value | -        | 9.0      | 16.0     | mA      |                                                        |

| Standby Current           | IDDs   | MODE-<br>"VSS", Other<br>input with<br>constant<br>voltage                                       | -        | 11.0     | 30.0     | μA      | VDD                                                    |

|                           |        | MODE-<br>"VDD", Other<br>input with<br>constant<br>voltage                                       | -        | 44.0     | 96.0     | - Fri ( |                                                        |

Product No.

DBC-32024041-1A0 REV. 1.1

Page 9 / 48

#### At "MODE" = "VSS"

#### (Unless otherwise noted, Ta=25°C, VDD=3.0V, VSS=0V)

| Item                     | Symbol | Condition       | Min  | Тур  | Max  | Unit | Applicable<br>terminal |

|--------------------------|--------|-----------------|------|------|------|------|------------------------|

|                          |        | VCOMDC[5:0]=00h | 0.94 | 1.04 | 1.14 | V    |                        |

| VcomDC<br>Adjusted value | VCOMDC | VCOMDC[5:0]=1Fh | 1.56 | 1.66 | 1.76 | V    | COMDC                  |

|                          |        | VCOMDC[5:0]=3Ch | 2.14 | 2.24 | 2.34 | V    |                        |

#### (Unless otherwise noted, Ta=25°C, VDD=3.0V, VSS=0V)

| Item                       | Symbol | Cond                                      | Min             | Тур  | Мах  | Unit |   |

|----------------------------|--------|-------------------------------------------|-----------------|------|------|------|---|

|                            |        | BRIGHT[5:0]=00h                           | D[*7:0]=00h     | 4.10 | 4.25 | 4.40 |   |

|                            |        | CONTRAST[3:0]=Eh                          | D[*7:0]=FFh     | 0.92 | 1.07 | 1.22 |   |

| BRIGHT                     | VLCD   | BRIGHT[5:0]=1Ah                           | D[*7:0]=00h     | 3.58 | 3.73 | 3.88 | V |

| Adjusted value             | VLCD   | CONTRAST[3:0]=Eh                          | D[*7:0]=FFh     | 0.40 | 0.55 | 0.70 | v |

|                            |        | BRIGHT[5:0]=2Eh                           | D[*7:0]=00h     | 3.18 | 3.33 | 3.48 |   |

|                            |        | CONTRAST[3:0]=Eh                          | D[*7:0]=FFh     | 0.00 | 0.15 | 0.30 |   |

|                            | VLCD   | CONTRAST [3:0]=0h<br>VLCD(D[*7:0]=00h)-VL | DC(D[*7:0]=FFh) | 1.35 | 1.50 | 1.65 |   |

| CONTRAST<br>Adjusted value |        | CONTRAST [3:0]=Eh<br>VLCD(D[*7:0]=00h)-VL | DC(D[*7:0]=FFh) | 3.03 | 3.18 | 3.33 | V |

|                            |        | CONTRAST [3:0]=Fh<br>VLCD(D[*7:0]=00h)-VL | DC(D[*7:0]=FFh) | 3.15 | 3.30 | 3.45 |   |

Product No. DBC-32024041-1A0 REV. 1.1

Page 10 / 48

# 3.3 INTERFACE PIN ASSIGNMENT

#### 3.3.1 LCM PIN Assignment

| Pin | Symbol  | Function                                                           |                                                                                           |  |  |  |  |

|-----|---------|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--|--|--|--|

| No. | Symbol  | Mode (No. 34 pin) = "VSS"                                          | Mode (No. 34 pin) = "VDD"                                                                 |  |  |  |  |

| 1   | VCOM    | Common-electrode driving signa                                     | l                                                                                         |  |  |  |  |

| 2   | D27     |                                                                    |                                                                                           |  |  |  |  |

| 3   | D26     | 7                                                                  | Display data (B)                                                                          |  |  |  |  |

| 4   | D25     | Display data (B)                                                   | 00h: Black                                                                                |  |  |  |  |

| 5   | D24     | 00h: Black                                                         | D22:LSB D27:MSB                                                                           |  |  |  |  |

| 6   | D23     | D20:LSB D27:MSB                                                    | Driver has internal gamma conversion.                                                     |  |  |  |  |

| 7   | D22     | <ul> <li>Driver has internal gamma</li> <li>conversion.</li> </ul> |                                                                                           |  |  |  |  |

| 8   | D21     |                                                                    | Short to VSS                                                                              |  |  |  |  |

| 9   | D20     |                                                                    | Short to VSS                                                                              |  |  |  |  |

| 10  | D17     |                                                                    |                                                                                           |  |  |  |  |

| 11  | D16     | 7                                                                  | Display data (G)                                                                          |  |  |  |  |

| 12  | D15     | Display data (G)                                                   | 00h: Black                                                                                |  |  |  |  |

| 13  | D14     | 00h: Black                                                         | D12:LSB D17:MSB                                                                           |  |  |  |  |

| 14  | D13     | D10:LSB D17:MSB                                                    | Driver has internal gamma conversion.                                                     |  |  |  |  |

| 15  | D12     | <ul> <li>Driver has internal gamma</li> <li>conversion.</li> </ul> |                                                                                           |  |  |  |  |

| 16  | D11     |                                                                    | Short to VSS                                                                              |  |  |  |  |

| 17  | D10     |                                                                    | Short to VSS                                                                              |  |  |  |  |

| 18  | D07     |                                                                    |                                                                                           |  |  |  |  |

| 19  | D06     |                                                                    | Display data (R)                                                                          |  |  |  |  |

| 20  | D05     | Display data (R)                                                   | 00h: Black                                                                                |  |  |  |  |

| 21  | D04     | 00h: Black                                                         | D02:LSB D07:MSB                                                                           |  |  |  |  |

| 22  | D03     | D00:LSB D07:MSB                                                    | Driver has internal gamma conversion.                                                     |  |  |  |  |

| 23  | D02     | <ul> <li>Driver has internal gamma</li> <li>conversion.</li> </ul> |                                                                                           |  |  |  |  |

| 24  | D01     |                                                                    | Short to VSS                                                                              |  |  |  |  |

| 25  | D00     |                                                                    | Short to VSS                                                                              |  |  |  |  |

| 26  | BLON    | Logic signal output for external<br>backlight circuitry            | OPEN                                                                                      |  |  |  |  |

| 27  | CS/STBY | CS: Chip select input for serial communication                     | STBY: Standby signal (Lo:<br>Normal operation, Hi: Standby)                               |  |  |  |  |

| 28  | DI/DE   | DI: Data input for serial<br>communication                         | DE: Input data effective signal                                                           |  |  |  |  |

| 29  | SCK/REV | SCK: Clock input for serial communication                          | REV: Right/Left & Up/Down<br>display reverse (Lo: normal<br>display, Hi: reverse display) |  |  |  |  |

| 30  | VSYNC   | Vertical sync signal input                                         | Vertical sync signal input<br>(negative polarity)                                         |  |  |  |  |

| 31  | HSYNC   | Horizontal sync signal input                                       | Horizontal sync signal input<br>(negative polarity)                                       |  |  |  |  |

| 32  | CLK     | Clock input signal                                                 | Clock input signal                                                                        |  |  |  |  |

| 33  | VSS     | GND                                                                |                                                                                           |  |  |  |  |

| 34  | MODE    | Input specification selection inpu                                 | t                                                                                         |  |  |  |  |

Product No. DBC-32024041-1A0 REV. 1.1

Page 11 / 48

| 35 | POCB   | Power On clear (Lo: active)                      |

|----|--------|--------------------------------------------------|

| 36 | NC     | OPEN                                             |

| 37 | RVDD   | Internal power supply                            |

| 38 | COMDC  | Common-electrode drive DC output                 |

| 39 | NC     | OPEN                                             |

| 40 | VSREF  | Built-in DAC reference supply                    |

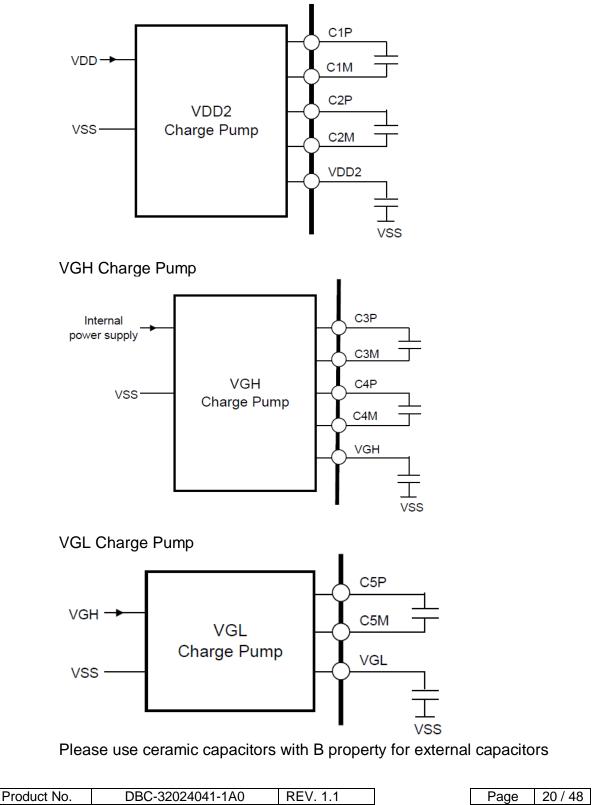

| 41 | C1P    | Contacting terminal of capacitor for charge pump |

| 42 | C1M    | Contacting terminal of capacitor for charge pump |

| 43 | C2M    | Contacting terminal of capacitor for charge pump |

| 44 | C2P    | Contacting terminal of capacitor for charge pump |

| 45 | VDD    | Power supply input                               |

| 46 | COMOUT | Square wave output for common-electrode          |

| 47 | VDD2   | Internal power supply                            |

| 48 | VSS    | GND                                              |

| 49 | VSS    | GND                                              |

| 50 | VSS    | GND                                              |

| 51 | C3M    | Contacting terminal of capacitor for charge pump |

| 52 | C3P    | Contacting terminal of capacitor for charge pump |

| 53 | C4M    | Contacting terminal of capacitor for charge pump |

| 54 | C4P    | Contacting terminal of capacitor for charge pump |

| 55 | VVCOM  | Voltage output for COMOUT                        |

| 56 | NC     | OPEN                                             |

| 57 | NC     | OPEN                                             |

| 58 | VGH    | Positive supply for gate driver                  |

| 59 | C5P    | Contacting terminal of capacitor for charge pump |

| 60 | C5M    | Contacting terminal of capacitor for charge pump |

| 61 | VGL    | Negative supply for gate driver                  |

| 62 | BLL2   | LED drive power source 2 (Cathode side)          |

| 63 | BLH2   | LED drive power source 2 (Anode side             |

| 64 | NC     | OPEN                                             |

| 65 | NC     | OPEN                                             |

| 66 | BLH1   | LED drive power source 1 (Anode side)            |

| 67 | BLL1   | LED drive power source 1 (Cathode side           |

Kyocera Elco 6281 series [04 6281 267 2x2 846+] Hirose Electric FH26 series [FH26G-67S-0.3SHBW(05)] Recommended connector:

As FCB cable has gold plated terminals, gilt finish contact shoe connector is recommended.

Product No.

DBC-32024041-1A0 REV. 1.1 Page 12 / 48

# 3.4 TIMING CHARACTERISTICS

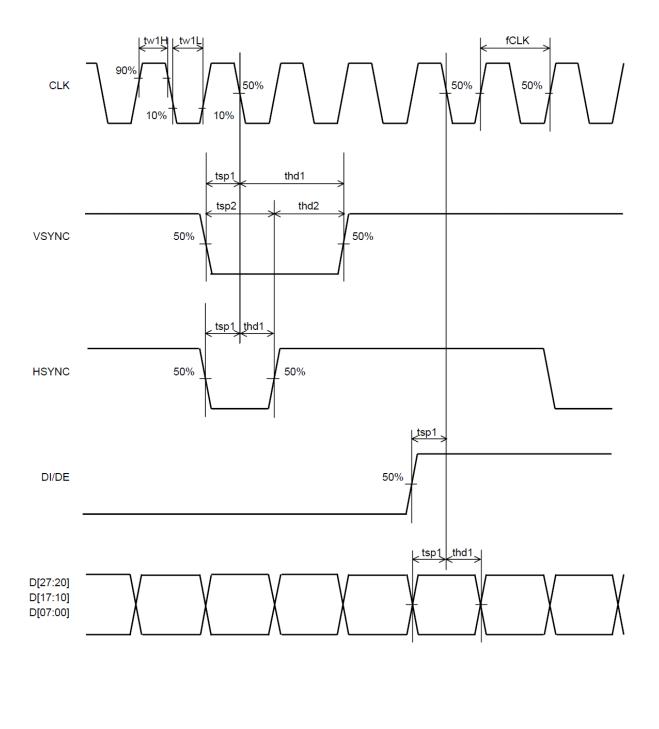

#### 3.4.1 AC Timing Characteristics

| (Unless otherwise noted, Ta = 25°C, VDD = 3.0V, VSS = 0V |        |                    |     |        |     |      |                                                         |  |  |

|----------------------------------------------------------|--------|--------------------|-----|--------|-----|------|---------------------------------------------------------|--|--|

|                                                          |        |                    |     | Rating |     |      | Annlinghla                                              |  |  |

| ltem                                                     | Symbol | Condition          | MIN | TYP    | MAX | Unit | Applicable<br>terminal                                  |  |  |

| CLK Low<br>period                                        | tw1L   | 0.1xVDD or<br>less | 20  | -      | -   | ns   | CLK                                                     |  |  |

| CLK High<br>period                                       | tw1H   | 0.9xVDD or<br>more | 20  | -      | -   | ns   | OLK                                                     |  |  |

| Setup time 1                                             | tsp1   |                    | 10  | -      | -   | ns   | CLK,<br>VSYNC,<br>HSYNC,                                |  |  |

| Hold time 1                                              | thd1   |                    | 10  | -      | -   | ns   | D[27:20],<br>D[17:10],<br>D[07:00],<br>DI/DE<br>[Note1] |  |  |

| Setup time 2                                             | tsp2   |                    | 2   | -      | -   | CLK  | VSYNC,                                                  |  |  |

| Hold time 2                                              | thd2   |                    | 2   | -      | -   | CLK  | HSYNC                                                   |  |  |

| CLK<br>frequency                                         | fCLK   |                    | -   | 6.75   | 9.0 | MHz  | CLK                                                     |  |  |

(Unless otherwise noted. Ta =  $25^{\circ}$ C. VDD = 3.0V. VSS = 0V)

| Product No.         DBC-32024041-1A0         REV. 1.1         Page | 13 / 48 |

|--------------------------------------------------------------------|---------|

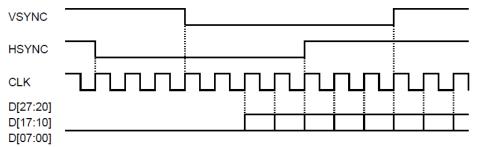

# 3.4.2 AC Timing Diagrams

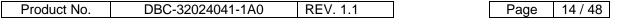

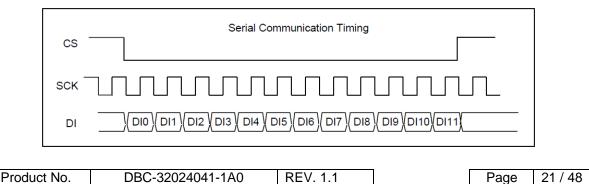

## 3.4.3 Serial Communication Block (at "MODE" = "VSS")

|                          |        |           |     | Rating |     |      | Applicable             |  |

|--------------------------|--------|-----------|-----|--------|-----|------|------------------------|--|

| ltem                     | Symbol | Condition | MIN | TYP    | MAX | Unit | Applicable<br>terminal |  |

| CS setup time            | tsp3   |           | 20  | -      | -   | ns   | CS/STBY                |  |

| CS hold time             | thd3   |           | 20  | -      | -   | ns   | 03/3151                |  |

| DI setup time            | tsp4   |           | 20  | -      | -   | ns   | DI/DE                  |  |

| DI hold time             | thd4   |           | 20  | -      | -   | ns   | DI/DE                  |  |

| CS pulse high<br>period  | tw4H   |           | 20  | -      | -   | ns   | CS/STBY                |  |

| SCK pulse low period     | tw5L   |           | 20  | -      | -   | ns   | SCK/REV                |  |

| SCK pulse high<br>period | tw5H   |           | 20  | -      | -   | ns   | SCK/REV                |  |

(Unless otherwise noted,  $Ta = 25^{\circ}C$ , VDD = 3.0V, VSS = 0V)

Note: unless otherwise noted, each item is defined between each 50% point of signal amplitude.

| Product No. | DBC-32024041-1A0 | REV. 1.1 | Page | 15 / 48 |

|-------------|------------------|----------|------|---------|

|             | •                |          |      |         |

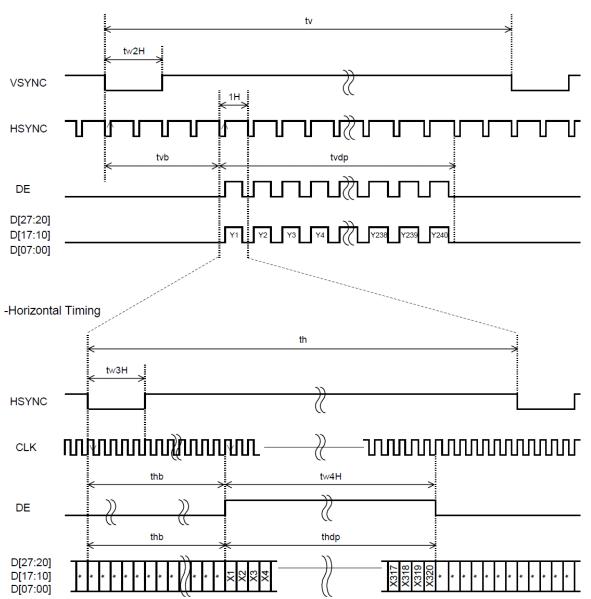

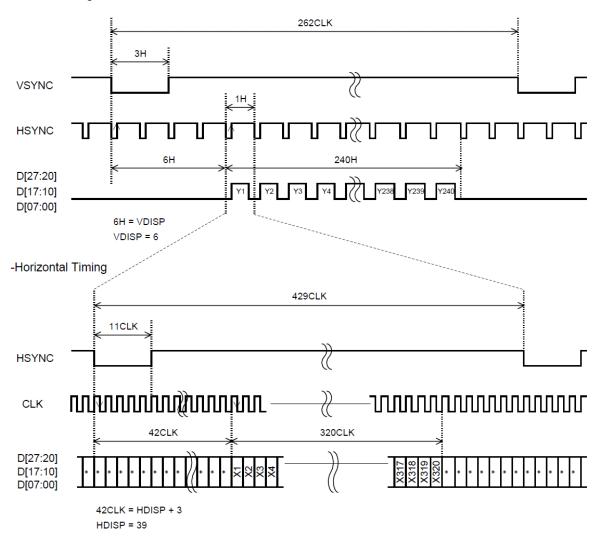

## 3.4.4 Input Timing Characteristics

#### MODE = "VSS"

| Item                      | Symbol |            | Rating |      | Unit | Applicable terminal                           |

|---------------------------|--------|------------|--------|------|------|-----------------------------------------------|

| liem                      | Symbol | MIN        | TYP    | MAX  | Unit | Applicable terminal                           |

| CLK frequency             | fCLK   | -          | 6.75   | 9.0  | MHz  | CLK                                           |

| VSYNC frequency Note1     | fVSYNC | 54         | 60     | 66   | Hz   | VSYNC                                         |

| Number of Frame Line      | tv     | -          | 262    | 291  | Н    | VSYNC,HSYNC                                   |

| VSYNC pulse width         | tw2H   | 4CLK       | ЗH     | -    |      | VSYNC,CLK                                     |

| Vertical back porch       | tvb    | 0<br>Note2 | 6      | 31   | н    | VSYNC, HSYNC,<br>D[27:20], D[17:10],          |

| Vertical display period   | tvdp   | -          | 240    | -    | Н    | D[07:00]                                      |

| HSYNC frequency           | fHSYNC | -          | 15.7   | -    | KHz  | HSYNC                                         |

| HSYNC signal cycle time   | th     | -          | 429    | 573  | CLK  | HSYNC, CLK                                    |

| HSYNC pulse width         | tw3H   | 2CLK       | -      | 20µs |      | HOTNO, OLK                                    |

| Horizontal back porch     | thb    | 5          | 42     | -    | CLK  | HSYNC,CLK,<br>D[27:20], D[17:10],<br>D[07:00] |

| Horizontal display period | thdp   | -          | 320    | -    | CLK  | D[27:20], D[17:10],<br>D[07:00], CLK          |

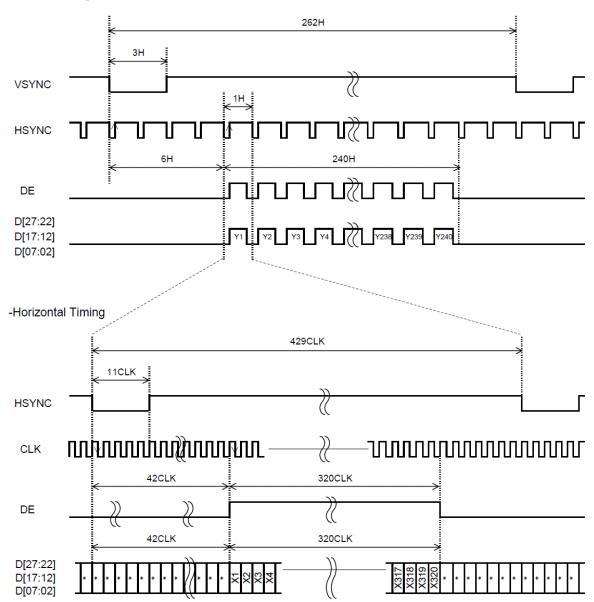

#### MODE = "VDD"

| Item                      | Symbol |            | Rating |             | Unit | Applicable terminal                               |

|---------------------------|--------|------------|--------|-------------|------|---------------------------------------------------|

| litem                     | Symbol | MIN        | TYP    | MAX         | Unit |                                                   |

| CLK frequency             | fCLK   | -          | 6.75   | 9.0         | MHz  | CLK                                               |

| VSYNC frequency Note1     | fVSYNC | 54         | 60     | 66          | Hz   | VSYNC                                             |

| Number of Frame Line      | tv     | -          | 262    | 291         | Н    | VSYNC,HSYNC                                       |

| VSYNC pulse width         | tw2H   | 4CLK       | ЗH     | -           |      | VSYNC,CLK                                         |

| Vertical back porch       | tvb    | 0<br>Note2 | 6      | 21<br>Note3 | н    | VSYNC, HSYNC,<br>DE, D[27:22],                    |

| Vertical display period   | tvdp   | -          | 240    | -           | Н    | D[17:12], D[07:02]                                |

| HSYNC frequency           | fHSYNC | -          | 15.7   | -           | KHz  | HSYNC                                             |

| HSYNC signal cycle time   | th     | -          | 429    | 573         | CLK  | HSYNC, CLK                                        |

| HSYNC pulse width         | tw3H   | 2CLK       | -      | 20µs        |      | HSTNC, CLK                                        |

| Horizontal back porch     | thb    | 5          | 42     | 77<br>Note3 | CLK  | HSYNC,CLK, DE,<br>D[27:22], D[17:12],<br>D[07:02] |

| DE Pulse Width            | tw4H   | -          | 320    | -           | CLK  | DE, CLK                                           |

| Horizontal display period | thdp   | -          | 320    | -           | CLK  | D[27:22], D[17:12],<br>D[07:02], CLK              |

Note 1: This is recommended spec to get high quality picture on display.

Note 2: When Vertical Back Porch is "0" please use odd number for the setting of the total number of lines that compose one field.

Note 3: when DE keeps "Lo" for 21H and 77CLK or longer, start capturing data automatically from "22H and 78 CLK".

Product No. DBC-32024041-1A0 REV. 1.1

Page 16 / 48

# 3.4.5 Driving Timing Chart

-Vertical Timing

| Product No. | DBC-32024041-1A0 | REV. 1.1 | Page | 17 / 48 |  |

|-------------|------------------|----------|------|---------|--|

|             |                  |          |      |         |  |

# 3.4.6 Example of Driving Timing Chart

### MODE = "VSS" (fCLK = 6.75MHz)

-Vertical Timing

| Product No. | DBC-32024041-1A0 | REV. 1.1 |   | Page | 18 / 48 |

|-------------|------------------|----------|---|------|---------|

|             |                  |          | - |      |         |

# 3.4.7 Example of Driving Timing Chart

### MODE = "VDD" (fCLK = 6.75MHz)

-Vertical Timing

Product No.

DBC-32024041-1A0

A0 REV. 1.1

Page 19 / 48

# 3.5 DESCRIPTION OF OPERATION

## 3.5.1 Power Supply

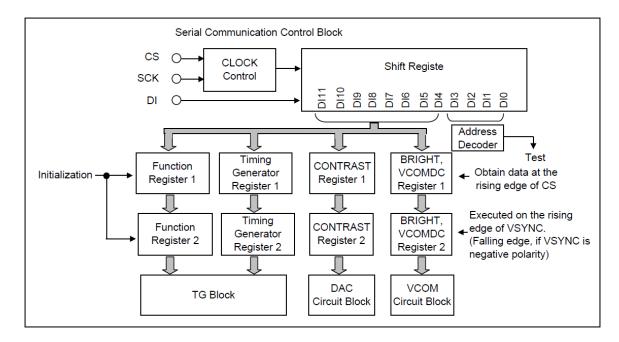

### 3.5.2 Serial Communication

Serial communication control function is effective at "MODE" = "VSS".

#### Feature Description

Serial communication control block is consist of registers that store data entered from CS, SCK, DI terminals and DAC that outputs control voltages to each part according to the data loaded from these registers. All registers are set to initial values at power-on. Electrostatics or noises may re-set the registers to improper values.

It is advisable to set up serial communication as frequently as possible as liquid crystal could degrade if such state is left untreated for a long time.

#### Serial Communication Timing

After input signal of CS drops from Hi to Lo, the Shift Resister loads 12 bits of serial data from DI at the rising edge of the input signal of SCK.

Mode register and DAC register load the stored data at the rising edge of the input signal of CS. When loaded DI data during the low period of CS is less than 12 bits, all loaded data are discarded.

When loaded DI data during the low period of CS is 12 bits or more, the last read of 12 bits is used .Each command is executed by VSYNC immediately after the rising the edge of CS. Serial Communication Control Block is configurable at any time during display and standby mode as it is completely independent from other circuitry run by CLK in the monitor.

# 3.5.2.1 Serial Communication Data

Configuration of serial data for DI terminal

| First |          |        |     |     |     |     |     |     |     |      | Last |

|-------|----------|--------|-----|-----|-----|-----|-----|-----|-----|------|------|

| LSB   |          |        |     |     |     |     |     |     |     |      | MSB  |

| DIO   | DI1      | DI2    | DI3 | DI4 | DI5 | DI6 | DI7 | DI8 | DI9 | DI10 | DI11 |

|       | Register | addres | s   |     |     |     | Da  | ata |     |      |      |

|          |     |     |      |     |               | LSB             |     |     |     |                    |     |      | MSB  | LSB |              |        |         |        |        |      | MSB    |

|----------|-----|-----|------|-----|---------------|-----------------|-----|-----|-----|--------------------|-----|------|------|-----|--------------|--------|---------|--------|--------|------|--------|

| Register |     | Add | ress |     | Number of     | of Preset value |     |     |     | User setting value |     |      |      |     |              |        |         |        |        |      |        |

|          | DI0 | DI1 | DI2  | DI3 | bits for data | DI4             | DI5 | DI6 | DI7 | DI8                | DI9 | DI10 | DI11 | DI4 | DI5          | DI6    | DI7     | DI8    | DI9    | DI10 | DI11   |

| BRIGHT   | 0   | 0   | 0    | 0   | 6 (DI6-DI11)  | -               | -   | 0   | 1   | 0                  | 1   | 1    | 0    | -   | -            |        | ι       | Jser   | settin | g    |        |

| VCOMDC   | 1   | 0   | 0    | 0   | 6 (DI6-DI11)  | -               | -   | 1   | 1   | 1                  | 1   | 1    | 1    | -   | -            | Optii  | mum     | settir | ig for |      | onitor |

| CONTRAST | 0   | 1   | 0    | 0   | 4 (DI4-DI7)   | 0               | 1   | 1   | 1   | -                  | -   | -    | -    | ι   | Jser s       | settin | g       | -      | -      | -    | -      |

| PANEL1   |     |     |      |     | 3 (DI9-DI11)  | -               | -   | -   | -   | •                  | 0   | 0    | 1    | •   | -            | -      | -       | -      | 0      | 0    | 1      |

| VDISP    | 1   | 1   | 0    | 0   | 5 (DI4-DI8)   | 1               | 0   | 1   | 0   | 1                  | -   | -    | -    |     | Use          | er set | ting    |        | -      | -    | -      |

| PANEL2   |     |     |      |     | 3 (DI9-DI11)  | -               | -   | -   | -   | -                  | 0   | 0    | 0    | -   | -            | -      | -       | -      | 0      | 0    | 0      |

| HDISP    | 0   | 0   | 1    | 0   | 8 (DI4-DI11)  | 0               | 1   | 0   | 1   | 0                  | 0   | 1    | 0    |     | User setting |        |         |        |        |      |        |

| PANEL3   | 1   | 0   | 1    | 0   | 8 (DI4-DI11)  | 0               | 1   | 0   | 0   | 1                  | 1   | 0    | 0    | 0   | 1            | 0      | 0       | 1      | 1      | 0    | 0      |

| FUNC1    | 0   | 1   | 1    | 0   | 8 (DI4-DI11)  | 0               | 0   | 0   | 1   | 0                  | 0   | 0    | 0    | 0   | ι            | Jser s | setting | g      | 0      | 0    | 0      |

| FUNC2    | 1   | 1   | 1    | 0   | 8 (DI4-DI11)  | 1               | 1   | 1   | 1   | 0                  | 0   | 0    | 0    | Use | er set       | ting   | 1       | 0      | 0      | 1    | -      |

| FUNC3    | 0   | 0   | 0    | 1   | 8 (DI4-DI11)  | 0               | 0   | 0   | 0   | 0                  | 0   | 0    | 0    | 0   | 0            |        | ι       | Jser   | settin | g    |        |

| FUNC4    | 1   | 0   | 0    | 1   | 8 (DI4-DI11)  | 1               | 0   | 0   | 0   | 0                  | 0   | 0    | 0    | 1   |              |        | Use     | er set | ting   |      |        |

| PANEL4   | 0   | 1   | 0    | 1   | 8 (DI4-DI11)  | 0               | 0   | 0   | 0   | 0                  | 0   | 0    | 0    | 0   | 0            | 0      | 0       | 0      | 0      | 0    | 0      |

| PANEL5   | 1   | 1   | 0    | 1   | 8 (DI4-DI11)  | 0               | 0   | 0   | 0   | 0                  | 0   | 0    | 0    | 0   | 1            | 0      | 0       | 0      | 0      | 0    | 0      |

| PANEL6   | 0   | 0   | 1    | 1   | 8 (DI4-DI11)  | 0               | 0   | 0   | 0   | 0                  | 0   | 0    | 0    | 0   | 0            | 0      | 0       | 0      | 0      | 0    | 0      |

| PANEL7   | 1   | 0   | 1    | 1   | 8 (DI4-DI11)  | 0               | 0   | 0   | 0   | 0                  | 0   | 0    | 0    | 0   | 0            | 0      | 0       | 0      | 0      | 0    | 0      |

| PANEL8   | 0   | 1   | 1    | 1   | 8 (DI4-DI11)  | 0               | 0   | 0   | 0   | 0                  | 0   | 0    | 0    | 0   | 0            | 0      | 0       | 0      | 0      | 0    | 0      |

| PANEL9   | 1   | 1   | 1    | 1   | 8 (DI4-DI11)  | 0               | 0   | 0   | 0   | 0                  | 0   | 0    | 0    | 0   | 0            | 0      | 0       | 0      | 0      | 1    | 0      |

#### Configuration of FUNC1 Register

| bit  | Function                | Description                                                                  |

|------|-------------------------|------------------------------------------------------------------------------|

| DI4  | TEST 0                  | Please fix it to "0".                                                        |

| DI5  | Vertical flip display   | Flip image vertically (from top to bottom). 0: Normal, 1: Vertical flip      |

| DI6  | Horizontal flip display | Flip image horizontally (from side to side). 0: Normal, 1: Horizontally flip |

| DI7  | Backlight control       | Set BLON signal that controls external backlight circuitry. 0: Low 1: High   |

| DI8  | Standby control         | Switch between standby and operation. 0: standby, 1: operation               |

| DI9  | TEST 1                  |                                                                              |

| DI10 | TEST 2                  | Please fix it to "0".                                                        |

| DI11 | TEST 3                  |                                                                              |

#### Configuration of FUNC2 Register

| bit  | Function       | Description                                                          |

|------|----------------|----------------------------------------------------------------------|

| DI4  | HSYNC polarity | Change polarity of HSYNC. 0: Positive polarity, 1: Negative polarity |

| DI5  | VSYNC polarity | Change polarity of VSYNC. 0: Positive polarity, 1: Negative polarity |

| DI6  | CLK polarity   | Change polarity of CLK. 0: Noninversion 1: Inversion                 |

| DI7  | TEST 4         | Please fix to "1".                                                   |

| DI8  | TEST 5         | Please fix it to "0".                                                |

| DI9  | TEST 6         |                                                                      |

| DI10 | Unused         | •                                                                    |

| DI11 | Unused         |                                                                      |

Product No.

DBC-32024041-1A0

0 REV. 1.1

Page 22 / 48

23 / 48

#### Configuration of FUNC3 Register

| bit  | Function | Description                                                                     |

|------|----------|---------------------------------------------------------------------------------|

| DI4  | Test 7   | Please fix it to "0".                                                           |

| DI5  | Test 8   |                                                                                 |

| DI6  | GM1[0]   | Register for gamma potential correction when input data D [*7:*0] is 192(=C0h). |

| DI7  | GM1[1]   |                                                                                 |

| DI8  | GM1[2]   |                                                                                 |

| DI9  | GM2[0]   | Register for gamma potential correction when input data D[*7:*0] is 148(=94h).  |

| DI10 | GM2[1]   |                                                                                 |

| DI11 | GM2[2]   |                                                                                 |

#### Configuration of FUNC4 Register

| bit  | Function         | Descrip                                                                         | tion                                 |  |  |  |

|------|------------------|---------------------------------------------------------------------------------|--------------------------------------|--|--|--|

| DI4  | Test 9           | Please fix to "1".                                                              |                                      |  |  |  |

| DI5  | Select gamma     | Select gamma correction curves. 0: buil                                         | t-in gamma correction curve          |  |  |  |

|      | correction curve | 1: use                                                                          | r-established gamma correction curve |  |  |  |

| DI6  | GM3[0]           | Register for gamma potential correction when input data D [*7:*0] is 108(=6Ch). |                                      |  |  |  |

| DI7  | GM3[1]           |                                                                                 |                                      |  |  |  |

| DI8  | GM3[2]           |                                                                                 |                                      |  |  |  |

| DI9  | GM4[0]           | Register for gamma potential correction when ir                                 | nput data D[*7:*0] is 64(=40h).      |  |  |  |

| DI10 | GM4[1]           |                                                                                 |                                      |  |  |  |

| DI11 | GM4[2]           |                                                                                 |                                      |  |  |  |

#### -TEST 0 to TEST 9

Please fix DI4, DI9 through DI11 of the FUNC1 registers to "0".

Please fix DI7 of FUNC2 to "1", DI8 and DI9 of FUNC2 to "0". DI10 and DI11 are no connection.

Please fix DI4 and DI5 of FUNC3 to "0".

Please fix DI4 of FUNC4 to"1".

#### -User Setting Values

Please use "User setting values" to set up PANEL1 through PANEL9, DI4, DI9 through DI11 of FUNC1, DI7 through DI9 of FUNC2, DI4, DI5 of FUNC3 and DI4 of FUNC4. Use of unspecified values may cause malfunction

| Product No. | DBC-32024041-1A0 | REV. 1.1 | Page |

|-------------|------------------|----------|------|

|             |                  |          |      |

### 3.5.3 Detailed Description of Functions

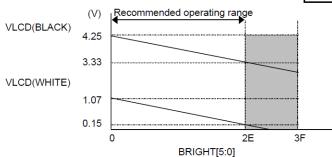

(1) Bright Control (BRIGHT)

Bright setting values is controlled by 6 bit (DI6 through DI1) of BRIGHT registers. The display lightens in proportion to data value while VLCD changes inversely with the data value. Initial value of BLACK[00h] is 3.73V and WHITE[FFh] is 0.55V when the CONTRAST register is Eh

The amount of change in VLDC is 0.02V per LSB

Recommended Operating Range The register shall be set in 00h to E2h range

|             |             |             | -  |

|-------------|-------------|-------------|----|

| BRIGHT[5:0] | VLCD(BLACK) | VLCD(WHITE) |    |

| 00h         | 4.25V       | 1.07V       | 1  |

| 01h         | 4.23V       | 1.05V       |    |

| ~           | ~           | ~           | Re |

| 1Ah         | 3.73V       | 0.55V       | ор |

| ~           | ~           | ~           |    |

| 2Dh         | 3.35V       | 0.17V       |    |

| 2Eh         | 3.33V       | 0.15V       | ↓  |

Recommended operating range

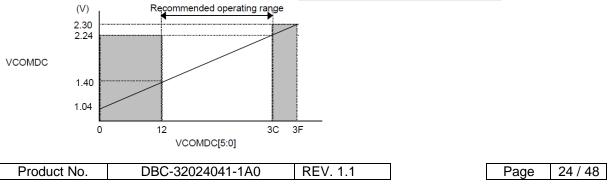

#### (2) Common Electrode Center Voltage (VCOMDC)

Common-electrode center voltage is controlled by 6-bit (DI6 through DI11). The voltage is proportional to data values. Each TFT monitor has to be optimized to its own optimum value separately. This optimization is mandatory. If not implemented, liquid crystal of TFT monitor will be degraded by long operation. Initial value of VCOMDC is 2.30V.(Typ.)

Amount of change in VCOMDC is 0.02V per LSB

**Recommended Operating Range**

Since VCOMDC has its optimum value somewhere between 1.40V and 2.24V, the register should be set in 12h to 3Ch range.

| VCOMDC[5:0] | VCOMDC (V) |       |

|-------------|------------|-------|

| 00h         | 1.04V      |       |

| ~           | ~          |       |

| 11h         | 1.38V      |       |

| 12h         | 1.40V      | ↑     |

| ~           | ~          | Rec   |

| 3Ch         | 2.24V      | ↓oper |

| ~           | ~          |       |

| 3Fh         | 2.30V      |       |

|             |            | •     |

|             |            |       |

Recommended operating range

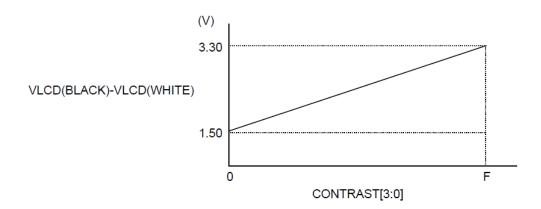

(3) Contrast Control (CONTRAST)

Contrast is controlled in 16 levels by 4-bit (DI4 through DI7) CONTRAST register. Contrast is proportional to data values. Contrast does not affect aforementioned bright control

Initial value of Contrast is 3.18V.Amount of change in contrast is 0.12V per LSB (Typ.)

|               | (')                     |

|---------------|-------------------------|

| CONTRAST[3:0] | VLCD(BLACK)-VLCD(WHITE) |

| 0h            | 1.50V                   |

| ~             | ~                       |

| Eh            | 3.18V                   |

| Fh            | 3.30V                   |

(4) Panel Setting 1 (PANEL 1)

PANEL 1 register 3-bit (DI9 to DI11) can select operating conditions from 8 choices. Please set this register to these values.

| DI9 | DI10 | DI11 |

|-----|------|------|

| 0   | 0    | 1    |

| [ | Product No. | DBC-32024041-1A0 | REV. 1.1 | ] | Page | 25 / 48 |

|---|-------------|------------------|----------|---|------|---------|

|   |             |                  |          | - |      |         |

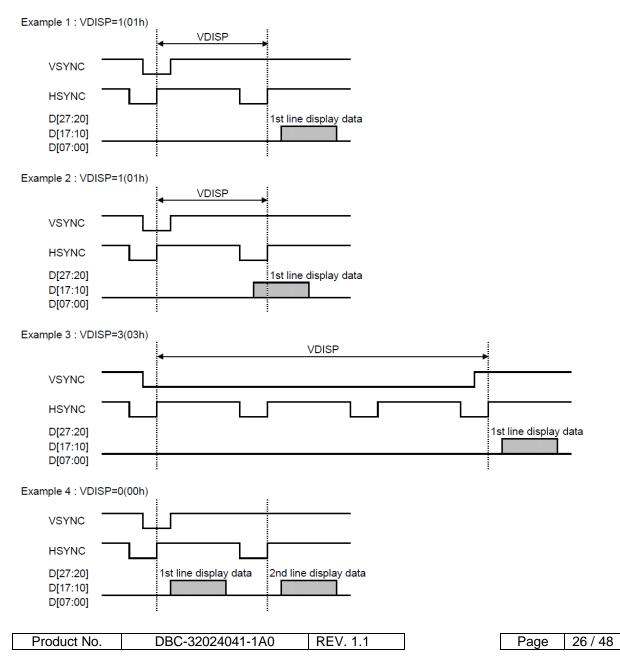

(5) Vertical Flyback Time Set (VDISP)

The length of vertical fly back period can be set from 0 to 31H by 5-bit of DI4 through DI8 of VDISP register. When VSYNC and HSYNC are negative polarity, "Lo" period of VSYNC is detected at the rising edge of HSYNC.

The setting value of VDISP is determined by the number of horizontal periods from the first detection of VSYNC=Lo to the first line's display data input. Please set VDISP=1 as shown in "Example 1" even if the display data of the first line is input

When the pulse width of VSYNC extends over two or more H as shown in "Example 3", the setting value is determined by the number of horizontal periods from the first detection of VSYNC=Lo to the first line's display data input.

When the initial value is "0", the first line's display data needs to be inputted immediately after VSYNC as shown in "Example 4".

When VDISP=0, please use odd number for the setting of the total number of lines that compose one field. This function can also be used for vertical display range setup (Vertical position setup).

(6) Panel Setting 2 (PANEL2)

PANEL 2 register 3-bit (DI9 and DI11) can select operating conditions from 8 choices. Please set this register to these values:

| DI9 | DI10 | DI11 |

|-----|------|------|

| 0   | 0    | 0    |

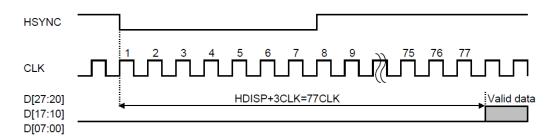

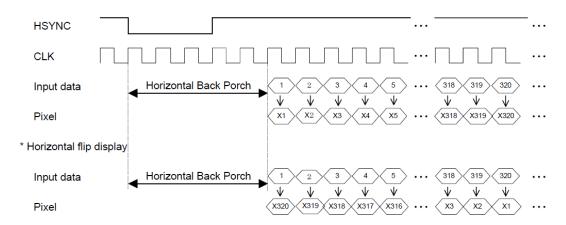

(7) Horizontal Flyback Period Setting (HDISP)

Horizontal flyback time can be set from 5 to 258CLK by HDISP register with 8-bit of DI14 thru DI11. However, set value of 0 or 1 is prohibited. Actual flyback time is "setting value plus 3CLK". When initial value is 74, a data after a lapse of 74 + 3CLK=77CLK from the rising edge of HSYNC is displayed as shown in the following chart.

This function can also be used for horizontal display range setup (Horizontal position setup). Example: HDISP=74(4Ah)

(8) Panel Setting 3 (PANEL3)

Select operating condition of the signal generated by driver IC in accordance with 8-bit of DI4 to DI11 of PANEL 3 register. Please set this register to these values.

| DI4 | DI5 | DI6 | DI7 | DI8 | DI9 | DI10 | DI11 |

|-----|-----|-----|-----|-----|-----|------|------|

| 0   | 1   | 0   | 0   | 1   | 1   | 0    | 0    |

| Product No. DBC-32024041-1A0 REV. 1.1 |

|---------------------------------------|

|---------------------------------------|

Page 27 / 48

#### (9) Function Set 1 (FUNC1)

FUNC1 register sets and controls the following functions by its each bit of DI5, DI6, DI7 and di8.

-Vertical Flip Display (Up/Down) DI5=0 for normal display, DI5 =1 for vertical flip display After completing the setup by serial communication, the selected display mode is carried out by VSYNC.

(Normal display is defined when FPC of the monitor is place downside.)

-Horizontal Flip Display (Right/Left)

DI6=0 for normal display, DI6=1 for horizontal flip display The selected display mode is executed at VSYNC after setup by serial communication.

(Please refer to the section 3.5.4. for Display Data Transfer)

-Backlight Control

DI7 switches the backlight driver IC. BLON terminal outputs set value of DI7.

Since its output level is VDD or VSS, this function can also be used for other controls than the backlight.

After completing the setup by serial communication, the selected display mode is carried out by VSYNC.

-Standby Mode

DI8=0 for standby mode, DI8 =1 for normal operation

Since default value of DI8 after power on is "0", it automatically goes to standby mode. Power consumption is significantly reduced in standby mode by disabling the timing generator and the LCD driving circuitry, and disconnecting current lines.

No image is displayed (white raster display) during standby mode unless DI8 is set to 1 for normal operation by serial communication. Serial data can be received by serial communication block even in standby mode.

Please refer to the section 3.5.5. "Standby (Power save) Sequence" for standby mode and power on/off sequence.

When normal operation is switched to standby mode, afterimage treatment is carried out before switching to standby mode.

| : No. DBC-32024041-1A0 REV. 1.1 |

|---------------------------------|

|---------------------------------|

Page 28 / 48

(10) Function Set 2 (FUNC2)

FUNC2 register sets and controls the following functions by its each bit of DI4 thru DI6.

-HSYNC, VSYNC, CLK Polarity Switching

Polarity of HSYNG is switched by DI4. DI4=0 for positive polarity input, DI4=1 for negative polarity input.

Polarity of VSYNC is switched by DI5. DI5=0 for positive polarity input, DI5=1 for negative polarity input.

Polarity of CLK is switched by DI6. DI6=0 for non-inversion, DI6=1 for inversion.

Initial value of DI4, DI5 and DI6 are "1". The following chart shows polarity of each signal at the initial value.

Please set change of VSYNC, HSYNC and display data at the rising edge of CLK.

Polarity of each signal can be changed independently by logic of DI4, DI5 and DI6.

Example 1 : DI4=0,DI5=DI6=1 (HSYNC has positive polarity and Hi active)

| VSYNC                                                  |                                                                       |              |

|--------------------------------------------------------|-----------------------------------------------------------------------|--------------|

| HSYNC                                                  |                                                                       |              |

| CLK                                                    |                                                                       |              |

| D[27:20]<br>D[17:10]<br>D[07:00]                       |                                                                       |              |

| Example 2 : DI4=1,                                     | DI5=0,DI6=1 (VSYNC has positive polarity and Hi active)               |              |

| VSYNC                                                  |                                                                       |              |

| HSYNC                                                  |                                                                       |              |

| CLK                                                    |                                                                       |              |

| D[27:20]<br>D[17:10]<br>D[07:00]<br>Example 3 : DI4=DI | I5=1,DI6=0 (CLK is reversed, data is read at the rising edge of CLK.) |              |

| VSYNC                                                  |                                                                       |              |

| HSYNC                                                  |                                                                       |              |

| CLK                                                    |                                                                       |              |

| D[27:20]<br>D[17:10]<br>D[07:00]                       |                                                                       |              |

| Product No.                                            | DBC-32024041-1A0 REV. 1.1                                             | Page 29 / 48 |

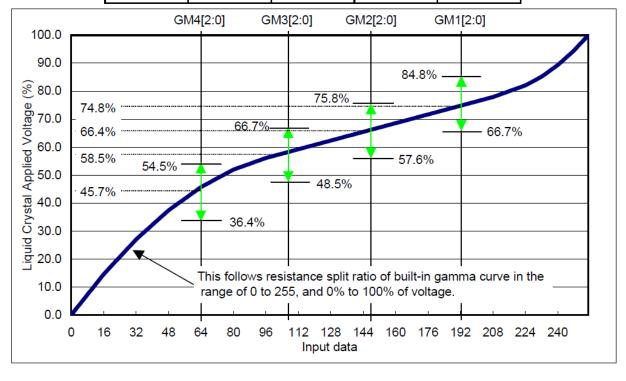

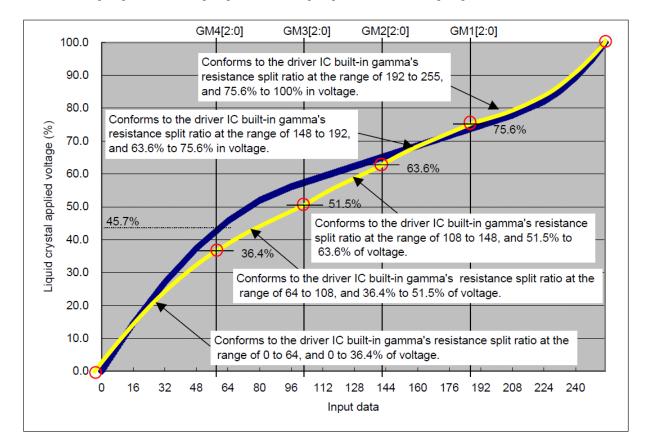

(11) Function Set 3, 4 (FUNC 3, 4)

-Gamma Curve Correction Select

| DI5=0 of FUNC 4 Register: | Deactivate user configurable gamma correction circuitry.                                                                             |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| DI5=1 of FUNC 4 Register: | Use built-in gamma curve.<br>Activate user configurable gamma correction circuitry.<br>Use user configurable gamma correction curve. |

-Setting Method of User Configurable Gamma Correction Curve

Gamma curve can be corrected by using GM1[2:0] thru GM4[2:0] registers of FUNC 3 and FUNC 4.GM1 thru GM4 corrects each following gamma potential respectively.

$GM1[2:0] \rightarrow Input data D[*7:*0] = Register for gamma potential correction at 192(=C0h)$  $GM2[2:0] <math>\rightarrow$  Input data D[\*7:\*0] = Register for gamma potential correction at 148(=94h) GM3[2:0]  $\rightarrow$  Input data D[\*7:\*0] = Register for gamma potential correction at 108(=6Ch) GM4[2:0]  $\rightarrow$  Input data D[\*7:\*0] = Register for gamma potential correction at 64(=40h)

Below chart shows characteristic curve of grey scale input data - liquid crystal applied voltage. Input value of "0" is assumed to be 0% of applied voltage to liquid crystal, and input value of "225" is assumed to be 100% of applied voltage to liquid crystal. Adjustable range of GM1 thru GM4 registers are described below.

|     | GM4[2:0]      | GM3[2:0]      | GM2[2:0]      | GM1[2:0]      |

|-----|---------------|---------------|---------------|---------------|

| 00h | No correction | No correction | No correction | No correction |

| 01h | 54.5%         | 66.7%         | 75.8%         | 84.8%         |

| 02h | 51.5%         | 63.6%         | 72.7%         | 81.8%         |

| 03h | 48.5%         | 60.6%         | 69.7%         | 78.8%         |

| 04h | 45.5%         | 57.6%         | 66.7%         | 75.6%         |

| 05h | 42.4%         | 54.5%         | 63.6%         | 72.7%         |

| 06h | 39.4%         | 51.5%         | 60.6%         | 69.7%         |

| 07h | 36.4%         | 48.5%         | 57.6%         | 66.7%         |

Product No.

DBC-32024041-1A0 REV. 1.1

Page 30 / 48

When no correction is made to gamma potential of GM1 to GM4;

The voltages at "0" and "255" are fixed in accordance with the contrast and brightness settings, and voltages at 1 to 254 are determined by resister split ratio produced by the driver IC built-in gamma curve resister. (Refer to the chart in previous page)

Liquid crystal applied voltage takes the values of 45.7%, 58.5%, 66.4% and 74,8% when input date is 64, 108, 148 and 192 respectively.

When correction is made to any of GM1 to GM4 by user;

The voltage is corrected in accordance with a correction point and its set value configured by user. The voltages at 1 to 254 are determined by resister split ratio between voltage at 0 and 225 and input data.

Example: Darken grey scale in black side.

- $\rightarrow$  Change liquid crystal applied voltage at the 64 point to darken side.

- $\rightarrow$  Set GM4[2:0] to 7h, GM3[2:0] to 6h, GM2[2:0] to 5h and GM1[2:0] to 4h.

(12) Panel Select 4 (PANEL 4)

Select operating condition of the signal generated by driver IC in accordance with 8-bit of DI4 to DI11 of PANEL 4 register. Please set this register to this value.

| DI4 | DI5 | DI6 | DI7 | DI8 | DI9 | DI10 | DI11 |

|-----|-----|-----|-----|-----|-----|------|------|

| 0   | 0   | 0   | 0   | 0   | 0   | 0    | 0    |

(13) Panel Select 5 (PANEL 5)

Select operating condition of the signal generated by driver IC in accordance with 8-bit of DI4 to DI11 of PANEL 5 register. Please set this register to this value.

| DI4 | DI5 | DI6 | DI7 | DI8 | DI9 | DI10 | DI11 |

|-----|-----|-----|-----|-----|-----|------|------|

| 0   | 1   | 0   | 0   | 0   | 0   | 0    | 0    |

(14) Panel Select 6 (PANEL 6)

Select operating condition of the signal generated by driver IC in accordance with 8-bit of DI4 to DI11 of PANEL 6 register. Please set this register to this value.

| DI4 | DI5 | DI6 | DI7 | DI8 | DI9 | DI10 | DI11 |

|-----|-----|-----|-----|-----|-----|------|------|

| 0   | 0   | 0   | 0   | 0   | 0   | 0    | 0    |

(15) Panel Select 7 (PANEL 7)

Select operating condition of the signal generated by driver IC in accordance with 8-bit of DI4 to DI11 of PANEL 7 register. Please set this register to this value.

| DI4 | DI5 | DI6 | DI7 | DI8 | DI9 | DI10 | DI11 |

|-----|-----|-----|-----|-----|-----|------|------|

| 0   | 0   | 0   | 0   | 0   | 0   | 0    | 0    |

(16) Panel Select 8 (PANEL 8)

Select operating condition of the signal generated by driver IC in accordance with 8-bit of DI4 to DI11 of PANEL 8 register. Please set this register to this value.

| DI4 | DI5 | DI6 | DI7 | DI8 | DI9 | DI10 | DI11 |

|-----|-----|-----|-----|-----|-----|------|------|

| 0   | 0   | 0   | 0   | 0   | 0   | 0    | 0    |

(17) Panel Select 9 (PANEL 9)

Select operating condition of the signal generated by driver IC in accordance with 8-bit of DI4 to DI11 of PANEL 9 register. Please set this register to this value.

| DI4 | DI5 | DI6 | DI7 | DI8 | DI9 | DI10 | DI11 |

|-----|-----|-----|-----|-----|-----|------|------|

| 0   | 0   | 0   | 0   | 0   | 0   | 1    | 0    |

| Product No. | DBC-32024041-1A0 | REV. 1.1 |  |

|-------------|------------------|----------|--|

|             |                  |          |  |

Page 32 / 48

### 3.5.4 Display Data Transfer

Input display data to D[27:20], D[17:10], D[07:00]. D\*0 : LSB, D\*7 : MSB

-Horizontal Timing and Order of Input Data

Display data shall be input in synchronization with CLK.

Polarity of CLK can be selected by DI16 of FUNCTION SET 2 (FUNC2).(at "MODE" = "VSS") Normal display: Normal display is defined as the orientation that the FPC cable on the TFT monitor is placed on the downside

-Vertical Timing and Order of Input Data

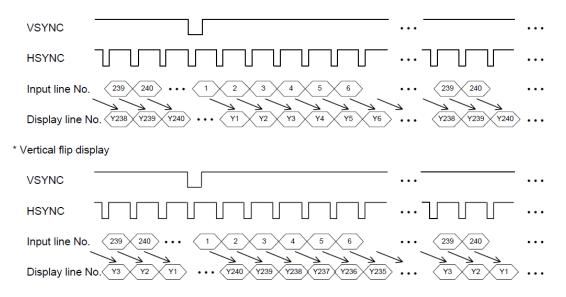

Transfer of display data that consist of 240 lines in 1 field is explained below. The correlations between input line and display line at normal display and vertical flip display are described below.

Normal display: Normal display is defined as the orientation that the FPC cable on the TFT monitor is placed on the downside.

\* Above timing charts show correlation between input data and pixels in visual way and it is not actual timing chart.

| Product No. DBC-32024041-1A0 REV. 1.1 | Page 33 / 48 |

|---------------------------------------|--------------|

|---------------------------------------|--------------|

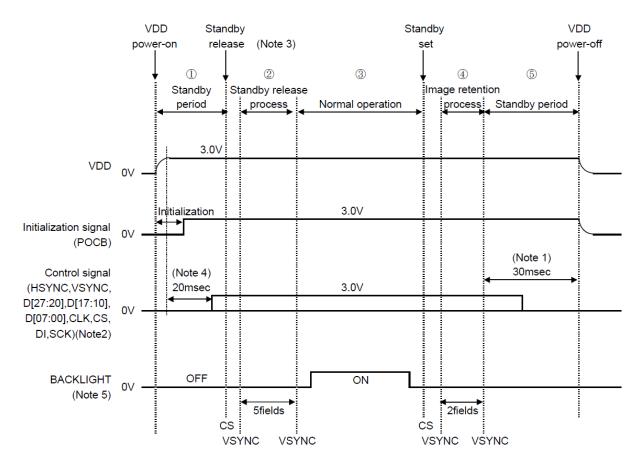

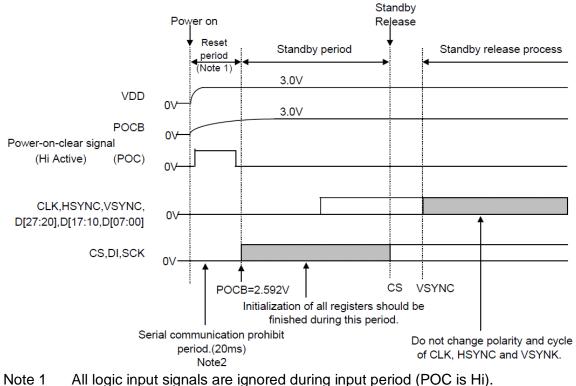

## 3.5.5 Standby (Power Save) Sequence

When "MODE" = "VSS", serial communication signals of CS, DI and SCK shall be input after VDD stabilizes at  $VDD \ge [0.9 \times VDD]V$  for more than 20 msec or more after power on. All initial values of serial data shall be set during this standby mode.

Other logic input signals of HSYNC,VSYNC,D[27:20],D[17:10],D[07:00] and CLK shall be input simultaneously after power on (specified period marked (1) in next page). All input signals shall be set to a fixed DC to reduce power consumption during standby mode.

Please follow the recommended power on/off sequence described below.

(1) Right after power on, serial communication registers are initialized. Therefore, standby control bit takes the value of "0". By this procedure the LCD goes into standby mode which significantly reduces power consumption of the LCD.

No image is displayed (white raster display) on the screen and internal power circuit is deactivated during standby mode.

Sync signal and display data (HSYNC,VSYNC,D[27:20],D[17:10],D[07:00],CLK) start to input before standby mode is released by serial communication.

(2) When the standby control bit is set to "1" by serial communication or the terminal "STBY" turn to "Lo" from "Hi", the standby mode is released by following VSYNC and the power supply circuit of building into begins operating.

No image is displayed (white raster display) on the screen for 5 fields from the following VSYNC after the release of standby mode.

③ LCD goes into normal display (display under normal operation) at the timing of VSYNC after completion of the procedure described in ②. Backlight shall be lit up 1 or more field after going to normal display.

(4) Standby mode can be established by setting standby control bit to "0" by serial communication or the terminal "STBY" turn to "Hi" from "Lo".

Display data is changed to FFh at VSYNC that comes right after this serial communication, and afterimage treatment is performed for 2 fields of VSYNC. Displayed image under normal display is immediately changed to white raster display by this treatment. Continue to input sync signal (HSYNC,VSYNC,CLK) during this period.

(5) LCD goes into standby mode, which is same as (1) above, at the timing of VSYNC after completion of the procedure described in (4). Serial communication data is retained during standby mode. Serial communication signal and input signal can be deactivated.

(2) to (4) repeats same procedures as described above.

Below procedure must be followed for power-off.

1 Implement standby setting.

2 After standby setting, continue to input sync signals (HSYNC, VSYNC, CLK) during the image treatment period (until VSYNC after 2 fields subsequent to standby setting).

(3) After (2), power off VDD after 30msec or more.

④ Stop the sync signals (HSYNC, VSYNC, CLK) subsequent to afterimage treatment period and no later than VDD off.

Product No.

DBC-32024041-1A0

REV. 1.1

Page

34 / 48

- Note 1:Power off VDD more than 30 msec after VSYNC that arrives 2 fields from standby set. Note 2:Input CLK during the period of inputting sync signals (HSYNC, VSYNC) and display data D[27:20],D[17:10],D[07:00].

- Note 3:Due consideration needs to be given to power supply capacity as bigger current (inrush current) flows at standby release.

- Note 4:Serial communication signals should be input after VDD stabilizes at VDD≧[0.9×VDD]V for more than 20 msec. And initial values of all serial data should be set during this period before standby release.

- Note 5:Backlight should be turned on after 5 fields from starting display. Backlight should be turned off before standby is set. Voltage values shown in this chart are typical values, not fixed values.

| Product No. | DBC-32024041-1A0 | REV. 1.1 | Page | 35 / 48 |

|-------------|------------------|----------|------|---------|

|             |                  |          |      |         |

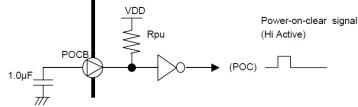

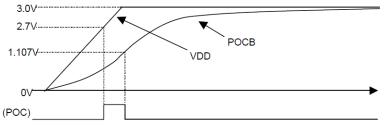

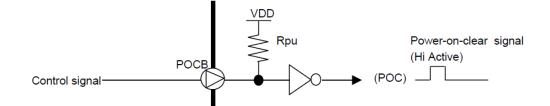

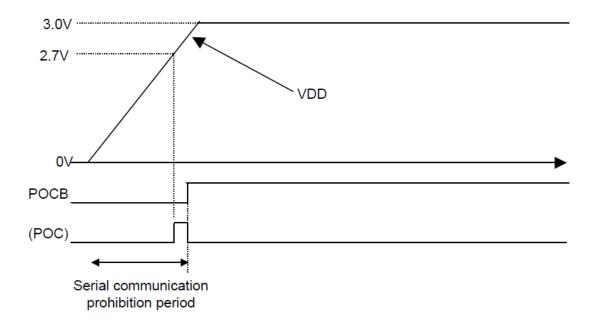

### 3.5.6 POWER ON SEQUENCE

There is the following limit between a power on period and the serial communication setting. Power-on-clear circuit diagram

FPOCB terminal is connected to VDD through the pull-up resistor (Rpu).

When rising of VDD takes long time, POCB will have unstable and unpredictable waveform. Please determine value of external capacitor by which POCB takes 1.107 V or less at VDD is 2.7V.

#### Power On Sequence

Serial Communication Prohibition Period

Note 1: All logic input signals are ignored during input period (POC is H). Note 2: Serial communication signals shall be input after VDD stabilizes at  $VDD \ge [0.9 \times VDD]V$  for more than 20 msec or more after power on.

| Product No. | DBC-32024041-1A0 | REV. 1.1 | Page | 36 / 48 |

|-------------|------------------|----------|------|---------|

|             |                  |          |      |         |

In case of rapid startup after power-on, directly control POCB terminal.

Power-on-clear circuit diagram

In case of directly controlling POCB terminal, POCB terminal should be set to "Lo" at Power-on POCB should be changed to "Hi" after VDD is exceeding 2.7V.Serial communication is prohibited while POCB is "Lo".

### 3.5.7 Other Functions

Built-in Panel Residual Charge Reduction Circuit

When the power turns off in accordance with the mandatory procedure described in the section "3.5.5. Standby (Power save) Sequence", afterimage treatment is carried out after standby mode is set. This circuit automatically reduces panel's residual charge and prevents afterimage for a long time even if standby mode setting fails to be made before power-off.

| Product No. | DBC-32024041-1A0 | REV. 1.1 |   | Page | 37 / 48 |

|-------------|------------------|----------|---|------|---------|

|             |                  |          | - |      |         |

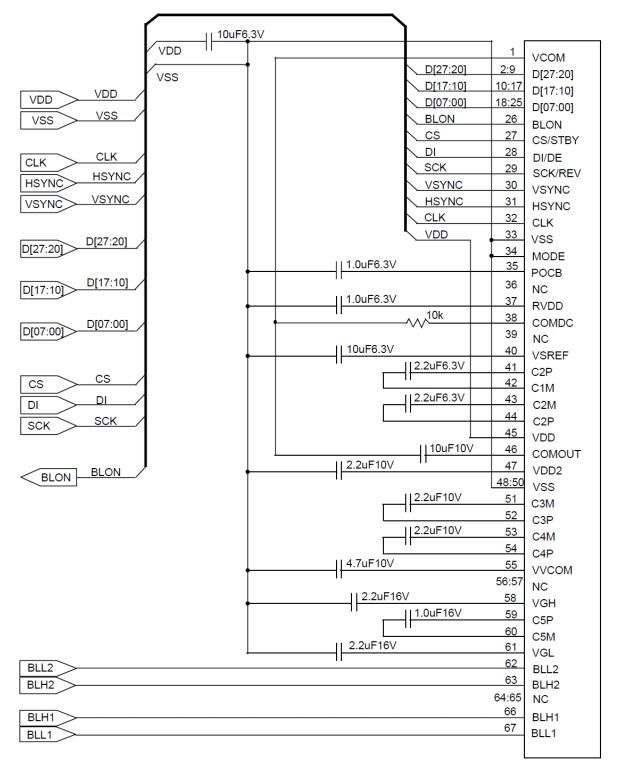

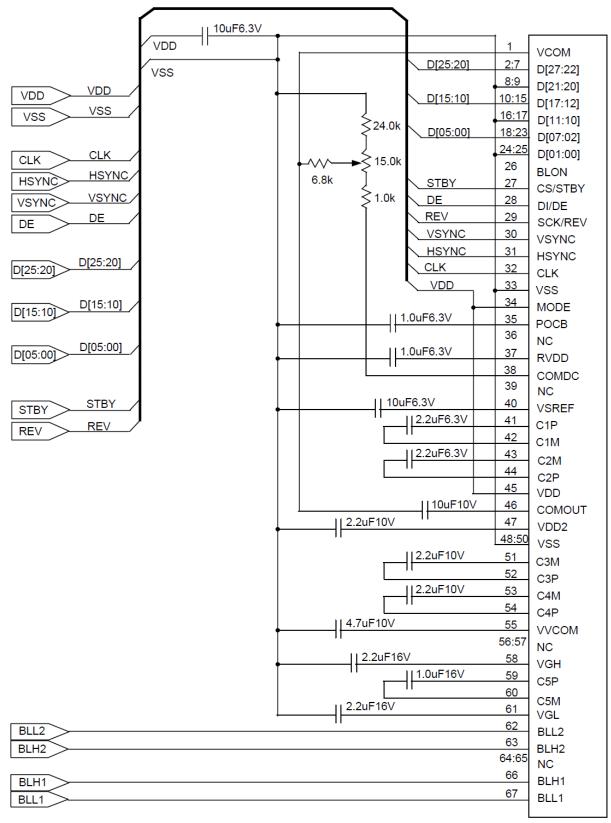

### 3.6 CIRCUIT

### 3.6.1 Driving circuit example (Module) ["MODE" = "VSS"]

#### TFT LCD MODULE REFERENCE CIRCUIT

This circuit is solely for reference purpose and optimum circuit and components values may be different. User's due consideration and evaluation must be given to this circuit design and component values prior to their intended use

| Product No. DBC-32024041-1A0 REV. 1.1 |  |

|---------------------------------------|--|

|---------------------------------------|--|

Page 38 / 48

### 3.6.2 Driving circuit example (Module) ["MODE" = "VDD"]

#### TFT LCD MODULE REFERENCE CIRCUIT

This circuit is solely for reference purpose and optimum circuit and components values may be different. User's due consideration and evaluation must be given to this circuit design and component values prior to their intended use

| Product No. | DBC-32024041-1A0 | REV. 1.1 |  |

|-------------|------------------|----------|--|

|-------------|------------------|----------|--|

Page 39 / 48

# **4 OPTICAL SPECIFICATION**

## 4.1 OPTICAL CHARACTERISTICS

|               |                         |                 |                           |                                                                                                                                         |      |                    |           | Ta = 25     | 5 °C |  |  |

|---------------|-------------------------|-----------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------|--------------------|-----------|-------------|------|--|--|

|               | Item                    | Symbol          | Condition                 | MIN                                                                                                                                     | ТҮР  | MAX                | Unit      | Note<br>No. | Note |  |  |

| onse<br>ne    | Rise Time.              | TON             | VLCD=<br>0.69V→3.87V      | -                                                                                                                                       | -    | 40                 | ms        | 1           | *    |  |  |

| Fall Time T   |                         | TOFF            | VLCD=<br>3.87V→0.69V      | -                                                                                                                                       | -    | 60                 | ms        |             |      |  |  |

| Backlight ON  |                         | Backlight ON CR |                           | 240                                                                                                                                     | 400  | -                  |           |             |      |  |  |

| Con<br>Ra     | Backlight OFF           | ÖK              | 0.69V/3.87V               | -                                                                                                                                       | 11.0 | -                  |           | 2           |      |  |  |

| 0             | Left                    | θL              |                           | 80                                                                                                                                      | -    | -                  | deg       | 3           | *    |  |  |

| Viewing Angle | Right                   | θR              | VLCD=<br>0.69V/3.87V      | 80                                                                                                                                      | -    | -                  | deg       |             |      |  |  |

| Viewing       | Up                      | φU              | 0.699/3.87V<br>CR ≥ 10    | 80                                                                                                                                      | -    | -                  | deg       |             |      |  |  |

| 1             | Down φΕ                 |                 |                           | 80                                                                                                                                      | -    | -                  | deg       |             |      |  |  |

|               |                         | V90             |                           | 0.8                                                                                                                                     | 1.1  | 1.4                | V         |             |      |  |  |

| V-T T         | T Threshold Voltage V50 |                 |                           | 1.3                                                                                                                                     | 1.6  | 1.9                | V         | 4           | *    |  |  |

|               | <u> </u>                |                 | V10                       |                                                                                                                                         |      | 1.8                | 2.1       | 2.4         | V    |  |  |

| White         | White V-T Curve         |                 | V-T Curve White V-T Curve |                                                                                                                                         |      |                    | Reference |             |      |  |  |

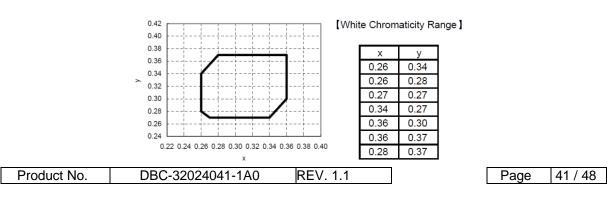

| \//bitc       | /hite Chromaticity      |                 |                           | White Chromoticity Panga                                                                                                                |      |                    |           | 5           |      |  |  |

| vviiite       | Chromaticity            | у               | VLCD= 0.09V               | VLCD= 0.69V White Chromaticity Range<br>No noticeable burn-in<br>image should be observed<br>after 2hours of window<br>pattern display. |      |                    |           | 5           |      |  |  |

| Burn          | in                      |                 |                           |                                                                                                                                         |      | observed<br>window |           | 6           |      |  |  |

| Centr         | re Brightness           | 1               | VLCD= 0.69V               | 250                                                                                                                                     | 350  | -                  | cd/m²     | 7           |      |  |  |

| Brigh         | tness Distribution      |                 | VLCD= 0.69V               | 70                                                                                                                                      | -    | -                  | %         | 8           |      |  |  |

\* < Measured in the form of LCD module.

<Measurement Condition>

Measuring instruments:

CS1000 (KONICA MINOLTA), LCD7000 OTSUKA ELECTRONICS), EZcontrast160D (ELDIM)

Driving condition:

VDD= 3.0V, VSS= 0V Optimized Vcom/c VLCD= | Vsigpp±Vcompp | /2